오늘은 버스에 대한 개념과, 버스를 설계하는 대표적인 두 가지 방법에 대해 설명합니다.

Bus

우리가 아는 버스와 비슷한 개념입니다. 우리가 버스를 타고 A에서 B로 이동하는 것처럼, 여기서 사용되는 Bus는 컴퓨터 내부에 있는 component들 사이에서 데이터를 전송하는 의사소통 시스템입니다.

실생활에서 버스의 노선을 굉장히 잘 잡는 것이 중요합니다. 이와 같이 이번에 배울 버스도 설계를 잘하는 것이 중요합니다. 그래야 데이터 사이의 충돌이 발생하지 않기 때문입니다. 따라서 우리는 Bus Master(bus에 의해서 전송되는 데이터)가 하나만 되도록 설계하는 것이 중요합니다.

Common Bus System

가장 기본적인 버스를 설계하는 2가지 방법에 대해서 알아봅시다.

1. Bus System with Multiplexer

첫 번째로는 MUX(MUltipleXer)를 이용하여 설계하는 방식입니다.

MUX란 여러 입력에 대해서 하나의 값만 선택하여 출력하는 장치입니다. 들어온 값들 중에서 control sign이 보내는 위치에 해당하는 값을 출력하게 됩니다.

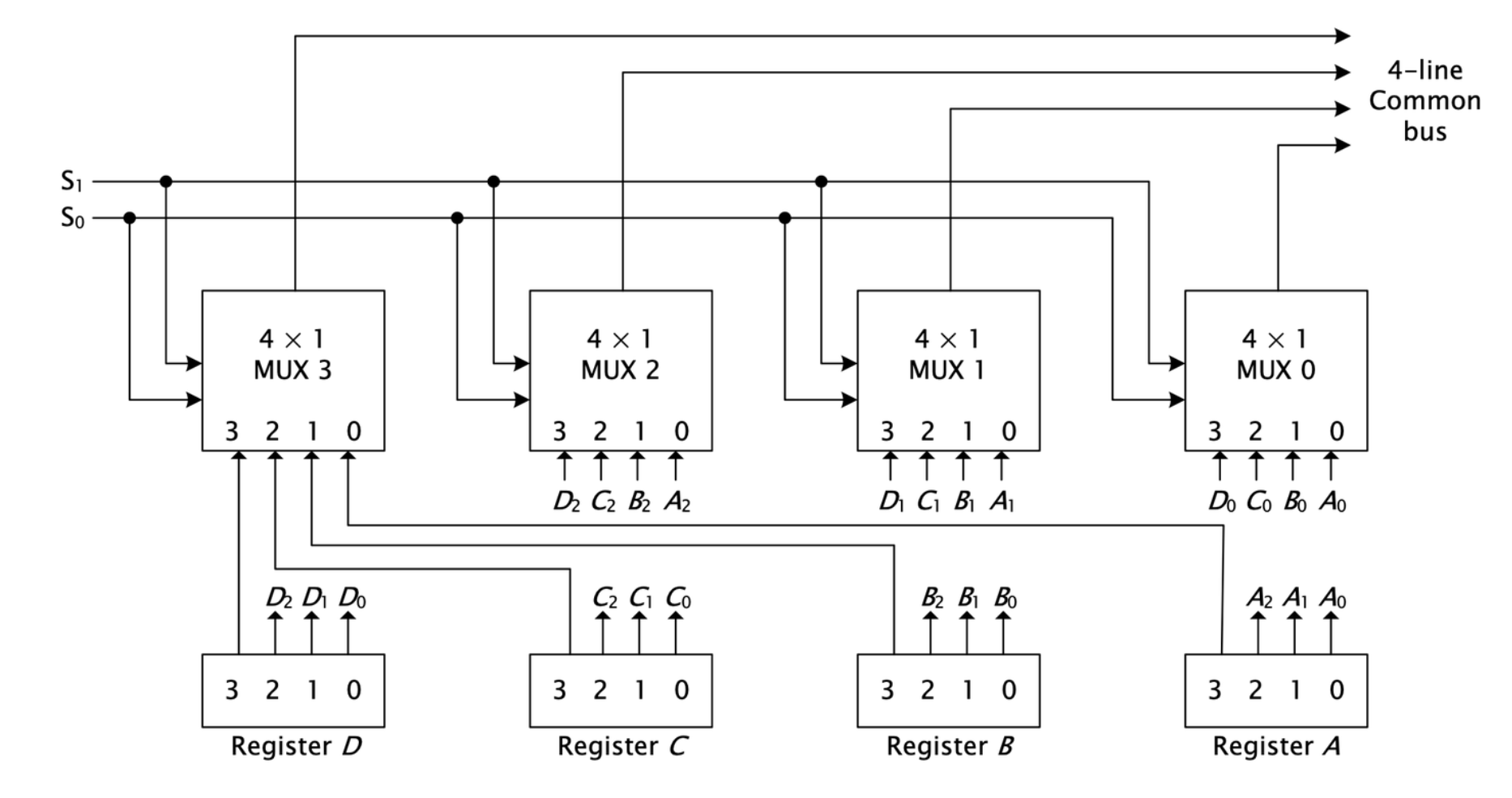

위는 MUX를 이용해서 설계한 Bus System입니다. MUX를 이용해서 설계하기 위해서는 MUX의 사이즈를 어떻게 정할 것인가, MUX의 개수는 몇 개여야 하는가에 대해서 생각해봐야 합니다.

n 개의 레지스터를 사용하고 있다면, MUX의 크기는 n x 1이 됩니다.

레지스터가 n-bit인 레지스터라면, MUX는 n개를 둡니다. 이 n에 따라서 control sign도 결정됩니다. 우리가 n-bit인 레지스터를 사용했으면, control sign은 n <= 2^x를 만족하는 가장 작은 x로 결정합니다. 위 사진에서는 x=2가 되겠습니다.

따라서 우리는 2개의 control sign과 4x1 MUX 4개를 두고 위와 같이 만들 수 있습니다.

위의 구조에 따라 아래의 진리표가 형성됩니다.

2번 째 경우인 S1 = 0, s0 = 1인 경우에 대해서 보겠습니다. 입력값이 01이므로 MUX는 들어온 A, B, C, D 중 01(= 십진수로 2)을 가르키는 B를 선택합니다. 따라서 이 버스는 레지스터 B가 선택되고, 이 때 B가 이 버스의 마스터가 됩니다.

2. Three-state bus buffers

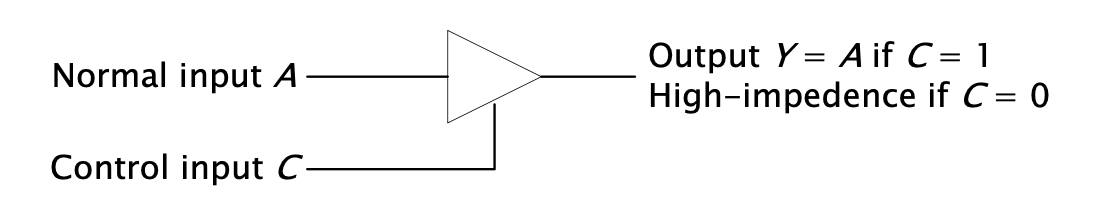

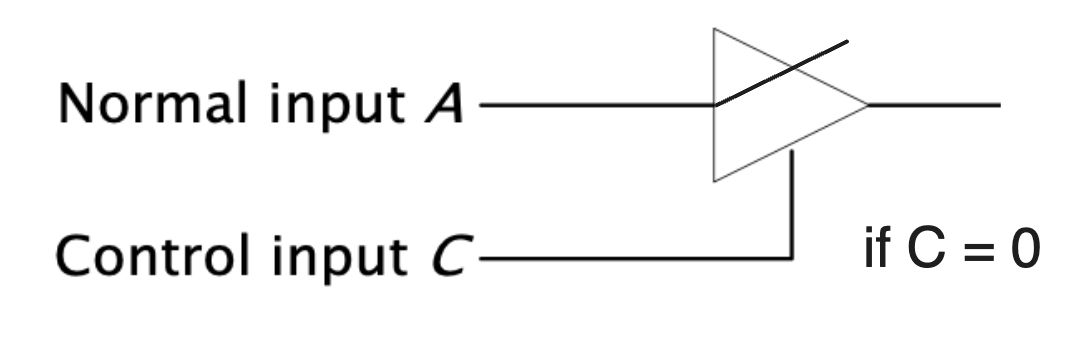

이를 알기 위해서는 우선, three-state-gate를 우선적으로 알아야합니다.

three-state-gate란 말그대로 3가지 상태를 가지는 디지털 회로를 말합니다. 이 회로는 0, 1, high-impednece 라는 세 종류의 상태를 가집니다.

high-impedent는 공중에 떠있는 상태를 말합니다. 따라서, C=0일 때는 아래와 같은 상태이기에 전달되지 않는다! 라고 이해하면 조금 더 쉬울 것 같습니다.

'CS > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조] 4-4. Logic μoperations (0) | 2023.09.24 |

|---|---|

| [컴퓨터구조] 4-3. Arithmetic μoperations (0) | 2023.09.16 |

| [컴퓨터구조] 4-1. Register Transfer (0) | 2023.09.14 |

| [컴퓨터구조] 3-3. Error Detection Codes (0) | 2023.09.13 |

| [컴퓨터구조] 3-2. Floating-Point Representation (0) | 2023.09.13 |